La icónica Ley de Moore, que ha guiado la evolución de la industria tecnológica durante casi seis décadas, enfrenta un desafío sin precedentes. La promesa de duplicar la cantidad de transistores en un chip cada 18 a 24 meses se está encontrando con límites físicos insalvables. A escalas nanométricas, los efectos cuánticos, las corrientes de fuga y la densidad térmica han convertido la miniaturización continua del silicio en una tarea con rendimientos decrecientes. Las frecuencias de los chips permanecen estancadas alrededor de los 5 GHz, y los avances por nodo tecnológico son cada vez más modestos, aunado al incremento en costos y complejidad que solo algunas fábricas pueden sostener.

Ante este panorama, mientras Occidente continúa perfeccionando los FinFETs y GAAFETs de silicio, un equipo de la Universidad de Pekín ha mostrado un avance que podría redefinir el futuro de la microelectrónica. Han desarrollado transistores GAAFET basados en materiales bidimensionales a partir de bismuto, integrados monolíticamente en 3D a bajas temperaturas. Su estudio, publicado en Nature Materials, sugiere que, en lugar de forzar el silicio una vez más, un cambio de enfoque puede ser más efectivo.

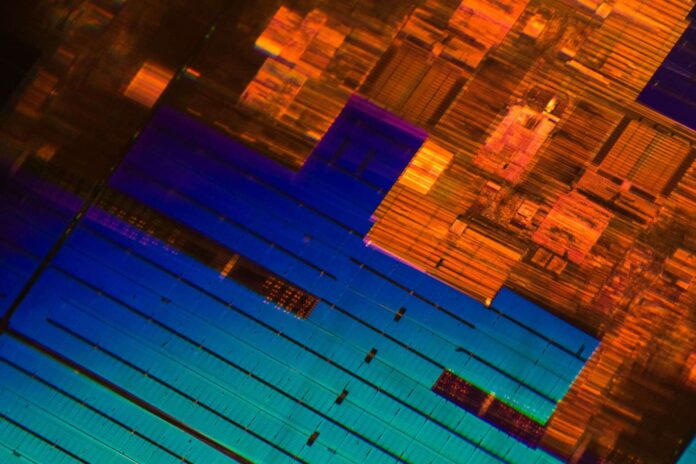

Este nuevo enfoque utiliza el Bi₂O₂Se como semiconductor canal y el Bi₂SeO₅ como dieléctrico de puerta, materiales que, sorprendentemente, trabajan en sinergia casi perfecta. La combinación de tecnología 2D, geometrías GAA y apilación monolítica 3D, permite reducir la tensión eléctrica y controlar mejor el canal, además de apilar funciones sin sobrecalentar la capa subyacente.

El silicio se acerca a sus límites. En un transistor nanométrico, los electrones comienzan a comportarse de manera impredecible a escala macro, generando túneles cuánticos a través del dieléctrico y aumentando las fugas incluso cuando el dispositivo está apagado. Esto lleva a un aumento de poder por área hasta niveles difíciles de disipar. La transición de geometrías planas a FinFET y luego a GAAFET ha mejorado el control electrostático, reduciendo fugas y permitiendo cierto margen de escalamiento, pero el material base sigue imponiendo restricciones.

El equipo de Pekín ha desarrollado un transistor GAAFET 2D utilizando el bismuto, donde el canal es un semiconductor 2D con alta movilidad de electrones y la puerta se aísla con un dieléctrico que crece a partir del propio canal. Esta configuración permite un control electrostático superior y una menor pérdida de energía.

La propuesta también permite una verdadera integración 3D monolítica, fabricando transistores conectados verticalmente en capas sucesivas sin recalentar las capas inferiores. Esta arquitectura acorta distancias entre lógica y memoria, reduce capacitancias parásitas y abre una vía para escalar en densidad sin depender de litografías cada vez más exigentes.

Sin embargo, este avance no está exento de desafíos. La transición de laboratorio a la producción industrial de alto rendimiento requiere controlar la variabilidad y el rendimiento por lote a gran escala. Además, la metalización y los contactos a canales 2D sin pines siguen siendo un reto, así como la necesidad de robustos modelos compactos para diseñadores.

El impacto potencial es significativo. La arquitectura de chips evolucionará, permitiendo una co-localización de lógica y memoria que podría reducir el cuello de botella entre la memoria y la CPU. Además, centros de datos podrían beneficiarse enormemente de una mayor eficiencia energética. A nivel geopolítico, el desarrollo de nuevos materiales 2D podría abrir nuevas cadenas de valor, desafiando el actual ecosistema centrado en el silicio.

Aunque la Ley de Moore tal como la conocemos podría estar transformándose, no está en absoluto obsoleta. La microelectrónica continúa evolucionando, y los materiales 2D junto con la integración 3D monolítica ofrecen nuevas oportunidades. El futuro apunta hacia una combinación de densidad vertical, menores voltajes y interfaces limpias, redefiniendo el avance tecnológico más allá de simples reducciones de escala.

Más información y referencias en Noticias Cloud.